- français

- English

AIC-mapper Progress Status

All details of the report can be seen in the svn documents, "svn\trunk\AIC_Mapper\Documents\AIC_Progress_Report.doc".

2014-04-22

- The repository environment has been built complete last week, and the details can be seen from the link: https://wiki.epfl.ch/aic/repository; The source codes and the document to explain the modification of data structures are upload.

- AIC-Mapper Progress Status

- Summary:cut-generation for LUT and AIC are both finished by now, but the cost function of delay and area only provide an interface, while the method inside the cost-function is no carefully considered yet.

- Details:

① Though we discuss that the first step focus on the cut-generation of AIC-only, however during the implementation, I found that the process of cut-generation for LUT and AIC are similar, there is no need to separate them, thus I directly implement “cut-generation” for both LUT and AIC;

② The cost-functions are not carefully considered because the value of Delay and Area only effect the sort of candidate cuts, but not affect the whole flow of mapping, so we left them as an interface and it can be left for future optimization;

③ By now, I’ve do some simple checks and test for the cut-generation part, but still cannot guarantee there are no bugs inside, so if you are interesting and can use the program to do some test, and if you find any bugs, email me, my email address: jiangbrave@126.com;

④ All addition source codes are under the directory of “src/map/if”, the file “ifAic.c, ifAic.h. if_test.c, if_test.h” are extra added comparing to original ABC codes. Other modifications are done directly on original codes, so no list here.

⑤ The all project are done under environment of Microsoft Visual Studio 2010, but I've modified the "Makefile" so the whole program can be compiled in Linux.

2014-04-30

Since last report, I’ve finish the process of Cut-Selection now. And nowadays, I’m dealing with the details inside the AIC-cut and it’s not finish yet.

Summary:

1. Since AIC is a complete subtree while AIG is a subgraph, so before mapping the AIG to AIC, I’ve to first turn the subgraph into a tree, and then make the tree complete. And by now, these two steps are done;

2. In AIC, except the first level, the configurable bit only exist at the output of an and-node, while in ABC, all inverter property is represented at the input of the And-node, thus I’ve to do some transformation to this, and this is done already;

3. After the two steps above, we can easily get the mask without too much effort, so a primary(not final) result of MASK can be generated now;

4. All functions list above are not tested, so my next schedule is to do some test of these functions.

2014-05-10

Summary:

1、 In last version of codes, all operations for AIC recovery are directly processed on original AIG netlist, which will lead to some problems. Therefore, I rewrite part of these codes;

2、 The whole AIC recovery process are finish in this version of codes, which the backward of mapping, and the mask information of nodes are complete;

Details:

1. In our mapper, the output level of an AIC can be specified by command option “-O”, however, this will lead to a question, see fig 1, if the output level is larger the depth of selected cut, the AIC-cut can’t directly output. Thus the Cut has to expand to the minimum depth that can be output. This is one of the reason that recovery cannot be done on original netlist which will change the original depth of AIG;

fig 1 The AIC-cut unable to output

2. Another major modification is the process of inverter of an CO(combinational Output)

In AIG, an CO can has an inverter input, which is meaning in graph but meaningless in physical circuit, thus some adjustments are done, see figure2 and figure3:

1) if it’s not the critical path, then a inverter is added, see figure 2;

figure 2. Add an inverter

2) if it’s on critical path, an inverter will increase the delay which bring bad effect on delay, thus the AIC node is duplicated to avoid an extra node on critical path. Instead duplicate the whole AIC node, we choose to just duplicate the minimum part of it which can be seen in figure 3;

figure 3. Duplicate the node if it’s on critical path

Plan:

1. Since the whole phase of mapping is complete now, the next step is to print it out in BLIF which can be sent to VPR for experiments;

2. Though the mask is done, but I don’t have good method to test whether it’s right, so after the print out function, I’ll start the equivalence check part;

2014-05-16

Summary:

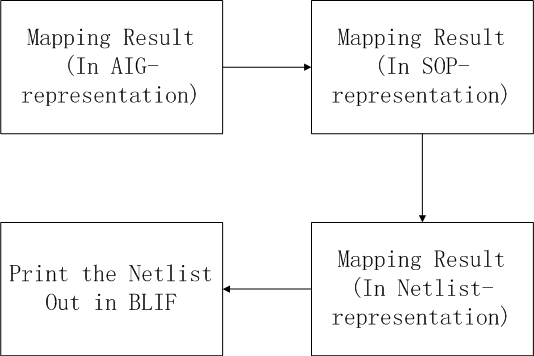

The major work this week is to try to print the mapping results into BLIF format. However, in ABC, between the mapping results and the printing out in BLIF, there are a few transformations need to be done for different data structures to represent the mapped netlist, shown in figure 1. By now, half work are done for this process.

Figure 1 The Process to print mapping result out in BLIF

Problem:

Since the codes for printing is not done yet, it cannot pass the flow, so I don’t update them to svn right now, which will be done when the printing is finish and pass the flow.

Plan:

Continue the process of the printing out, try to print it out in BLIF.

2014-06-06

Although delay for the other project, the output generation has been complete now. The source code has update to the svn, and a simple user guide for using mapper will be update to the document directory.

New funcitons:

1. Output generation to BLIF file is complete, and the mask information also finish;

2. The resynthesis is not support yet, so please don't use resynthesis commands, but if you think it necessary to do some resynthesis before mapping, I'll do some modification, but however it won't affect the procedure of mapping;

3. The AIC and LUT lib is support now, which is easy for us to modify the delay and area parameters ;

However, I don't have much time to done the testing, I just test the VTR benchmarks and make sure the generation of mapper pass the VPR flow using the arch files of yours. So please use this mapper to do the estimation, and if you have found any bugs in the mapper, please email me and I'll try to fix it.

2014-05-16

Some efforts have been done for the AIC-mapper in these days, which are list below:

1. As we known, there will be a middle-crossbar (e.g. x-inputs-y-outputs) after the AIC-output-pins which try to reduce the unnecessary output signals. This design is based on the concept that the valid outputs of an AIC node is much smaller than the physical outputs. However, if the valid outputs are larger than the value of Y, this design become incorrect which an AIC node can’t be packed into any clb due to the output constraints. Therefore, in the AIC-mapper, I add an extra parameter to constraint the vaild outputs of an AIC which make sure the valid outputs is not larger than Y. ( the parameter is set by option “-X”)

2. In last version of mapper, synthesis commands are not allowed before mapping, which I think not appropriate though it is helpless in mapping phase. However , the optimization before mapping is necessay. Thus, I make some change to make the optimization before mapping allowed. For example, cmd-“choice” is not allowed in last version of AIC-mapper, but allowed in the new release.

3. About the cost function: the cost functions in the mapper are kind of area-flow, may be not so accurate. And for the convenience of experiments, I extra the cost functions into an specific file named “ifAicCostFun.c”, all cost functions are list inside.

4. A bug of “Writing off the end of the array” is fixed in mapper.