- français

- English

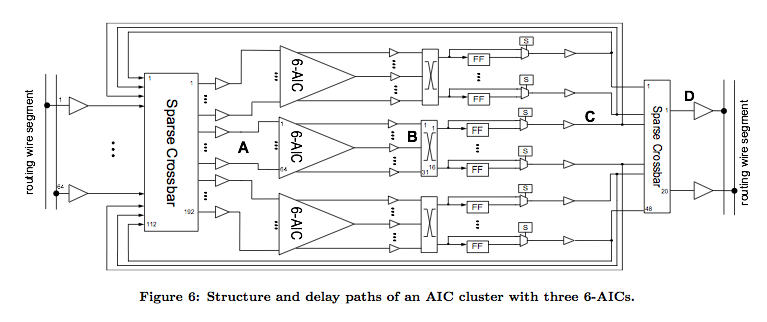

AIC cluster

Delays

The whole AIC_cluster is implemented exactly in the way the paper “Rethinking FPGA” shows. And I use the latest version of input crossbar. The delays I get after optimization are listed below. As the optimization is an endless work, you need to trade-off the area and delay. So these are primary delay parameters. If needed, I will sacrifice the area for the delay further.

A -> B 260ps

B -> C 197ps (delay of middle crossbar) + 62ps (delay of FF-Mux)

C -> D 282ps

Delay of input crossbar 283ps

The path is defined the same as the paper.

Area

Two methods are used to calculate the area of AIC_cluster. One takes the number of transistors as the unit, and the other takes the number of minimum width transistors as the unit. The statistics are shown below.

- In unit of the number of transistors

- Input crossbar 49152 (78.07%)

- AIC 6090 (9.67%)

- Middle crossbar 3504 (5.57%)

- DFF+mux 2112 (3.35%)

- Output crossbar 2100 (3.34%)

- Total 62 958

- In unit of the number of minimum width transistors

- Input crossbar 94220.16 (82.17%)

- AIC 7636.74 (6.66%)

- Middle crossbar 6219.36 (5.42%)

- DFF+mux 2991.84 (2.61%)

- Output crossbar 3595.8 (3.14%)

- Total 11 4663.9

Person in charge: Rachel