# Facile Five-Step Heteroepitaxial Growth of GaAs Nanowires on Silicon Substrates and the Twin Formation Mechanism

Maoqing Yao, Thunyang Sheng, Mingyuan Ge, Chun-Yung Chi, Sen Cong, Aiichiro Nakano, P. Daniel Dapkus, Aiichiro Nakano, Aiichiro Nakano, Dapkus, Aiichiro Nakano, Aiichiro Nakan

†Ming Hsieh Department of Electrical Engineering, ‡Collaboratory for Advanced Computing and Simulations, Department of Physics and Astronomy, Department of Computer Science, and Department of Chemical Engineering and Materials Science, 8Mork Family Department of Chemical Engineering and Materials Science, and || Center for Energy Nanoscience, University of Southern California, Los Angeles, California 90089, United States

Supporting Information

ABSTRACT: Monolithic integration of III-V semiconductors with Si has been pursued for some time in the semiconductor industry. However, the mismatch of lattice constants and thermal expansion coefficients represents a large technological challenge for the heteroepitaxial growth. Nanowires, due to their small lateral dimension, can relieve strain and mitigate dislocation formation to allow single-crystal III-V materials to be grown on Si. Here, we report a facile fivestep heteroepitaxial growth of GaAs nanowires on Si using selective area growth (SAG) in metalorganic chemical vapor deposition, and we further report an in-depth study on the twin formation mechanism. Rotational twin defects were observed in the nanowire structures and showed strong dependence on the growth condition and nanowire size. We adopt a model of faceted growth to demonstrate the formation of twins during growth, which is well supported by both a transmission electron microscopy study and simulation based on nucleation energetics. Our study has led to twin-free segments in the length up to 80 nm, a significant improvement compared to previous work using SAG. The achievements may open up opportunities for future functional III-V-on-Si heterostructure devices.

KEYWORDS: heteroepitaxy, GaAs on Si, nanowires, twin defect, MOCVD, thermodynamics, TEM

n recent years, semiconductor nanowires have attracted a great deal of research interest due to their unique electronic and optical properties. 1-8 III-V compound semiconductor nanowires possess advantages of high mobility, direct band gap, and the capability of band-gap engineering the properties over a wide range, making them promising candidates for future electronic, 9-17 optoelectronic, 18-28 and energy devices. 29-33 On the other hand, Si is still the dominant material in today's semiconductor industry because of its relatively low cost and mature processing technology. It thus has been a natural desire to integrate III-V semiconductors with Si to enable novel functional devices that can take advantage of the benefits offered by both materials. This technology could substantially influence the integrated circuit industry by the monolithic integration of III-V materials and Si circuitry. Of no less importance to energy research is the development of multijunction solar cells using III-V materials grown on lowcost and sturdy Si substrates. 34-36

To achieve such integration in a thin film fashion represents a significant technological challenge caused by several problems

Received: November 16, 2015 Accepted: February 1, 2016 Published: February 1, 2016

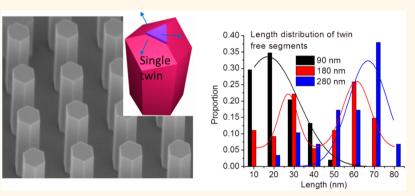

Figure 1. (a) Temperature profile of GaAs nanowire growth on Si (111). Red and blue blocks indicate the time  $AsH_3$  and TMG are supplied, respectively. (b) The  $30^{\circ}$  tilted and (c) top view SEM images of uniform GaAs nanowire arrays grown on Si. (d) Schematic diagram of a crystal lattice at the GaAs/Si interface, viewed from the [1-10] orientation. (e) HRTEM image taken at the GaAs/Si interface. Arrows indicate sites with misfit dislocation.

intrinsic to the interface of the two dissimilar materials. Mismatches in the lattice constants and thermal expansion coefficients can lead to misfit dislocations or even nonepitaxial growth. 37,38 The polar nature of the bonds in III-V materials makes the growth on nonpolar Si difficult and causes antiphase boundaries (APBs).<sup>39–42</sup> The native oxide layer commonly observed on the Si surface is another major factor hindering the epitaxial growth. 43-45 The use of nanowire geometry for GaAs on Si provides benefits in this integration owing to the small lateral dimension. Strain due to lattice mismatch can be effectively relieved in the lateral directions, 46-49 and the probability of forming APBs is remarkably reduced. Highquality single-crystal III-V nanowires grown on a Si substrate have been successfully demonstrated in recent years. 43-A wide range of applications have also been explored including high-speed transistors, 10 tunnel diodes, 75,76 light-emitting diodes (LEDs), 18,19,28 room-temperature lasers, 20 and solar cells.7

The vapor–liquid–solid (VLS) growth method, which was first developed by Wagner and others in 1960s and 1970s, <sup>78</sup> has become the most prevalent approach to grow III–V nanowires on Si substrates. Au is widely used as the catalyst due to the ease of preparation and low reactivity. Vertical nanowire arrays have been successfully obtained through Au-catalyzed VLS in molecular beam epitaxy (MBE)<sup>61,71,74</sup> and metalorganic chemical vapor deposition (MOCVD). <sup>43,58,60,62,63,73</sup> On the other hand, the use of Au during the growth <sup>79–81</sup> leads to the speculation that deep levels acting as recombination centers may be created. <sup>82</sup> Group III atom self-catalyzed VLS growth has thus attracted attention since no foreign metal intermixing is involved in this method. <sup>51–55,57,64–67</sup> However, the metal droplet places constraints on the growth of axial heterostructure with different group III elements. The droplet usually remains after growth due to the properties of VLS growth and is undesired in some applications such as efficient light extraction

in LEDs and good ohmic contact formation in solar cells. Significant progress has been made with non-VLS methods, including selective area growth (SAG)<sup>44,45</sup> and oxide-assisted self-induced growth. <sup>68,69</sup> In particular, pioneering work was done by Tomioka *et al.*<sup>44,45</sup> using SAG, where the nanowires were precisely located by a predefined array of openings in a dielectric mask and no catalyst was required. In Tomioka's work, they used a seven-step approach for the epitaxial growth of GaAs nanowires on Si, including (1) ramp-up of the sample temperature, (2) a thermal annealing at 925 °C to remove the native oxide, (3) ramp-down of the sample temperature to 400 °C, (4) surface treatment with only AsH<sub>3</sub> flow at 400 °C, (5) ramp-up of the sample temperature again to the growth temperature, (6) the GaAs growth at 750 °C, and (7) cooling the sample.

The high uniformity of nanowire morphology allows the fabrication of versatile devices in a controllable manner. Photodetectors,<sup>27</sup> LEDs,<sup>83</sup> and solar cells<sup>29,33</sup> have been achieved using nanowires. Nevertheless, rotational twins and polytypism are common defects observed in both VLS- and non-VLS-grown nanowires. These defects are believed to cause altered band structure in nanowires compared to their bulk counterpart. Carrier scattering, local quantum confinement, and nonintrinsic carrier transition processes are incurred due to the band discontinuity between zincblende (ZB) and wurtzite (WZ) regions.<sup>84–88</sup> Understanding the driving force for twin formation and control of its presence has become a topic of intense research. Substantial progress in eliminating twins and polytypism has been achieved for the VLS mode with a general agreement that the thermodynamics at the triple-phase interface line is the dominant factor controlling the defect formation. <sup>51,53,89–97</sup> The understanding of the twin formation mechanism in SAG mode is not fully understood yet and was interpreted from several different perspectives including faceted growth 98,99 and thermodynamics of nucleation. 87,100

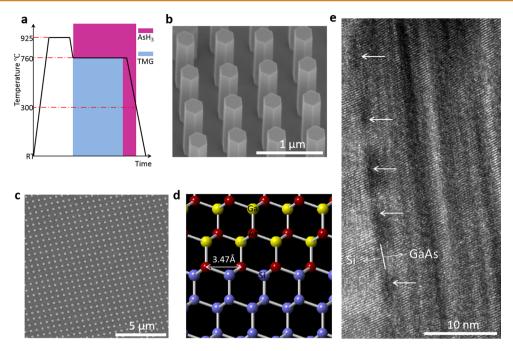

Figure 2. The 30° tilted SEM images at the mask openings on (a) GaAs (111)B and (b) Si (111) substrates after 2 min growth at 790 °C. (c) Top view SEM images of nuclei after 2 min growth at different temperatures and AsH<sub>3</sub> partial pressures; scale bar 200 nm. TMG partial pressure was kept constant at  $7.56 \times 10^{-7}$  atm. (d) Schematic of relevant low-index planes viewed from the  $\langle 111 \rangle B$  direction. (e) Projection of relevant low-index planes on the (1-10) plane in a GaAs zincblende lattice.

Here, we report a facile five-step heteroepitaxial growth of GaAs nanowires on Si (111) substrates using SAG and an indepth study of the twin formation mechanism. Our five-step approach eliminates the AsH $_3$  surface treatment step and the associated sample temperature ramping step, which offers simplified process flow and provides 100% nanowire yield and great uniformity. In addition, our in-depth study of the nanowire twin formation mechanism has led to the growth of twin-free GaAs nanowire segments up to a length of  $\sim$ 80 nm, which represents a significant improvement compared to  $\sim$ 42 monolayers ( $\sim$ 14 nm) reported in previous work.

### **RESULTS AND DISCUSSION**

We successfully used the facile five-step approach for heteroepitaxial growth of GaAs nanowires on Si (111) substrates using SAG. The growth steps are summarized in Figure 1a. Briefly, after substrate preparation, the Si (111) substrates are immediately loaded into the MOCVD reactor. Step 1 is to ramp up the temperature from room temperature to 925 °C for hydrogen annealing. Step 2 is to keep the temperature stable at 925 °C and anneal the substrates in hydrogen ambient for 5 min to remove native oxides. Step 3 is to ramp down the temperature directly to the desired growth temperature between 700 and 790 °C, and for the case shown in Figure 1a, the temperature is 760 °C. Step 4 is the step when the nanowires grow. Precursors including trimethylgallium (TMG) and arsine (AsH<sub>3</sub>) are introduced simultaneously at the

beginning of the step, and the temperature is kept at the growth temperature. During this step, the nanowires would grow in the vertical GaAs (111)B direction. After the desired growth time (typically ~1 h), the final step is to close the TMG supply and cool the system while the AsH3 precursor continues to flow until the temperature is below 300 °C to prevent nanowire decomposition. Detailed substrate preparation and growth steps are described in the Methods. Figure 1b shows a scanning electron microscopy (SEM) image taken at a 30° tilted angle of nanowires grown at 760 °C. All the wires are located uniformly in the predefined template and exhibit a 6-fold symmetric cross section consisting of  $\{1-10\}$  sidewall facets. Figure 1c shows a top view SEM image of the nanowire array. The yield of vertical nanowires is 100%. Compared to the seven-step growth reported by Tomioka et al., 44,45 our five-step growth method could also give 100% yield and similarly high uniformity of nanowire morphology, while our direct heteroepitaxial growth without AsH<sub>3</sub> treatment could significantly simplify the growth temperature profile.

The lattice constants of Si and GaAs are different by 4.1%. GaAs nanowires with a small enough footprint can, however, be grown on Si coherently without generating misfit dislocations (MFDs) at the interface. Such a MFD-free interface was observed by Tomioka *et al.* when they grew GaAs on Si with an actual opening diameter of 19 nm. <sup>44</sup> For larger nanowires, the increased strain energy would lead to MFDs at the interface once the nanowires are beyond a critical size. Previous

calculations based on continuum elasticity have estimated the critical height and diameter of nanowires for MFD generation and shown considerable stress relief through MFDs. 48,101 The nanowires discussed in this paper fall into this category. As shown in Figure 1d, the distance between two adjacent As atoms in the [11-2] direction is 3.47 Å, and the lattice mismatch is 4.1%, so the period of MFD is 3.47 Å/0.041 = 8.46nm. To examine the crystal structure of our nanowires and the heteroepitaxial interface, we cut a 70 nm thin slice parallel to the  $\{1-10\}$  crystal planes from the center of a nanowire using a focused ion beam (JEOL). High-resolution transmission electron microscopy (TEM) images were taken with a [1-10] zone axis. A high density of twins was observed immediately after the growth started for nanowires grown at 760 °C in Figure 1e. The size of our nanowires is above the critical diameter and height for MFD-free growth, so periodic MFDs are observed at the GaAs/Si interface together with periodic contrast variation on the GaAs side due to strain distribution. The average period of the MFDs is 8.45 nm, which agrees with the calculated value based on the analysis above. Our measured period also agrees with the value calculated by Yuan et al. combining molecular-dynamics and quantummechanics simulations.

To initiate coherent epitaxial growth of GaAs nanowires on Si, previous studies indicate a nucleation or surface treatment step is often required prior to the nanowire growth. For the Aucatalyzed VLS growth, Kang et al. found vertical nanowires can be obtained only with high-temperature nucleation followed by low-temperature nanowire growth. 63 In the case of SAG, Tomioka et al. pointed out that the Si surface needs to be soaked in As ambient first to form Si (111):As surface reconstruction, which is an analogue of a GaAs or InAs (111)B surface. To prevent As evaporation from this surface, lowtemperature surface treatment in AsH3 was performed prior to ramping up the temperature for the nanowire growth. 44,45 However, we used direct heteroepitaxial growth without AsH<sub>3</sub> treatment, which simplified the temperature profile of the growth procedure to just five steps (Figure 1a). On the contrary, as shown in the Supporting Information (Figure S1), the surface treatment step at lower temperatures only decreased the vertical nanowire yield. Furthermore, high-yield vertical nanowires could be grown even on a Si surface exposed to dry etching, showing the robustness of our method. In our study, the sizes of the mask openings for samples prepared using electron beam lithography (EBL) and photolithography were around 100 and 200 nm, respectively. One possible mechanism that allows us to grow without low-temperature surface treatment could be the relatively large size of mask openings in our study compared to those reported in other papers. 44,45,63 Because the initial growth adopts a Volmer-Weber (island) mode, as will be shown later, abundant sources captured in large mask openings ensure an adequate local supply of adatoms on the nuclei and prevent them from decomposing.

To better understand the growth behavior at the initial stage, we grew nanowire material using the five-step growth method for only 2 min (defined by the TMG supply time) on both GaAs (111)B and Si (111) substrates and examined their nuclei morphologies under SEM. The SEM images show the nuclei formed in the mask openings after growth at 790 °C and 2.14 ×  $10^{-5}$  atm AsH<sub>3</sub> partial pressure (equivalent V/III ratio = 283) on a GaAs (111)B substrate (Figure 2a) and on a Si (111) substrate (Figure 2b). The material deposited on the GaAs substrate fills the entire opening and maintains a flat surface. In

contrast, the nuclei on the Si substrate appear to be islands with crystalline facets. The classic models to depict different film growth mechanisms are  $^{102}$  layer-by-layer growth (Frank–vander-Merve, or FM, mechanism), island growth (Volmer–Weber, or VW, mechanism), and the Stranski–Krastanov (SK) method (an initially continuous film that becomes islanded but with a thin continuous "wetting" layer left). The interplay among surface energies of the substrate  $(\gamma_s)$ , the film  $(\gamma_f)$ , and their interface  $(\gamma_i)$  decides the actual growth mechanism.  $^{99}$  If the substrate surface energy is smaller than the sum of the two other surface energies, the island growth (VW) occurs because the exposed substrate surface is energetically favorable:

$$\gamma_{\rm s} < \gamma_{\rm f} + \gamma_{\rm i}$$

whereas the reverse inequality,

$$\gamma_{\rm s} > \gamma_{\rm f} + \gamma_{\rm i}$$

is associated with layer-by-layer growth (FM).

Our result agrees with early studies that GaAs-on-Si growth occurs in the VW mode. 103-105 As-passivated Si (e.g., the Si (111):As surface mentioned earlier) was found to be highly inert (low  $\gamma_s$ ) due to the existence of As lone-pair states and was even shown to be almost unaffected by exposure to oxygen or air. 106 Previous studies have also shown that the growth temperature  $(T_g)$  and the AsH<sub>3</sub> partial pressure  $(P_{AsH3})$  can affect the shape of grown GaAs crystals during SAG MOCVD. So we varied  $T_{\rm g}$  between 670 and 790 °C and  $P_{\rm AsH3}$  between 2.14  $\times$  10<sup>-5</sup> and 1.43  $\times$  10<sup>-3</sup> atm while keeping the TMG partial pressure constant at  $7.56 \times 10^{-7}$  atm. Figure 2c shows the top view SEM images of typical nuclei under each growth condition. All the conditions result in VW growth, and a hexagonal cross section emerges after a short time. However, the growth rates along different orientations show strong dependence on both  $T_{\rm g}$  and  $P_{\rm AsH3}$ . In general, lateral growth is suppressed under lower  $P_{AsH3}$  or higher  $T_g$ , while the vertical growth is enhanced under these conditions. We believe this is related to the different  $T_g$  and  $P_{AsH3}$ dependence of the growth rate for different crystal planes. Figure 2d shows the relevant low-index planes viewed from the (111)B direction, and Figure 2e shows their orientations in relation to the zincblende GaAs crystal lattice viewed from the [1-10] direction. In crystal growth, facets are expressed because of their slow growth rate. At higher  $T_g$  and lower  $P_{AsH3}$ (those within the blue background in Figure 2c), the growth in the  $\langle 111 \rangle$ B direction is faster than in the  $\langle 1-10 \rangle$  directions, so the adatoms migrate to the top of nuclei and contribute to the vertical growth. The lateral growth is instead suppressed, and clear {1-10} sidewall facets can be seen due to their slow growth. The tilted  $\{-1-10\}$  facets have the same surface atomic configurations as those of  $\{1-10\}$  sidewalls, but due to adatom accumulation at the top, the growth in the tilted  $\langle -1-$ 10 $\rangle$  directions is still faster than that in the vertical <1-10 $\rangle$ directions. The tilted  $\{-1-10\}$  facets are not expressed, and the top surface is usually flat. However, in the extreme case of 790 °C  $T_{\rm g}$  and 2.14 × 10<sup>-5</sup>  $P_{\rm AsH3}$ , the nuclei tend to be pyramids enclosed by tilted  $\{-1-10\}$  facets, meaning the growth rates in those directions are also significantly reduced. In contrast, when  $T_g$  decreases and  $P_{AsH3}$  increases, the growth rate in the  $\langle 111 \rangle$ B direction decreases and those in the  $\langle 1-10 \rangle$ directions increase. The nuclei under these conditions (those within the pink background in Figure 2c) extend further laterally and show much smaller height than those grown under higher  $T_{\rm g}$  and lower  $P_{\rm AsH3}$ . The nuclei grown at 670 °C  $T_{\rm g}$  and

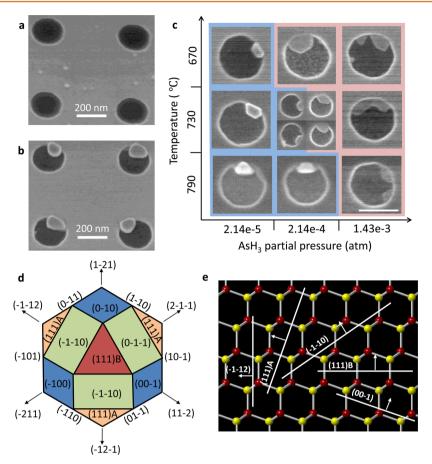

Figure 3. (a) The  $30^{\circ}$  tilted SEM images of nanowires grown at  $850^{\circ}$ C; the initial part was grown at  $760^{\circ}$ C to help nucleate. White circles indicate nanowires with a completely pinched-off tetrahedron tip, while red circles indicate nanowires with a triangular-shaped thin mesa surrounded by three tilted  $\{-1-10\}$  facets. (b) SEM images of nanowire tips with different morphologies; scale bar 200 nm. Images are organized in a sequence according to the twin formation model in (c). (c) Schematic of the twin formation process during nanowire growth. (d) TEM image of a region consisting of an even number of twins. The crystals at two sides of the transitional region share the same atomic registry. (e) SEM image of a nanowire tip. After an even number of twins, the wire pinches off. (f) TEM image of a region consisting of an odd number of twins. The crystal at two sides of the transitional region can be considered as rotated by  $180^{\circ}$  compared to each other. (g) SEM image of a nanowire tip with an odd number of twins.

$2.14 \times 10^{-3}$   $P_{\rm AsH3}$  are not as tall as the silicon nitride mask, while those grown at 790 °C  $T_{\rm g}$  and  $2.14 \times 10^{-5}$   $P_{\rm AsH3}$  are around 100 nm tall. Under low  $T_{\rm g}$  and high  $P_{\rm AsH3}$  conditions, due to the increased growth rates in the  $\langle 1-10 \rangle$  directions, the hexagonal cross sections are less obvious and multiple nuclei are observed. Variation of the growth rates in the  $\langle 111 \rangle$ B direction is believed to be dominated by the surface reconstruction that is related to As surface enrichment and is a strong function of  $T_{\rm g}$  and  $P_{\rm AsH3}$ . Ultra-high-vacuum studies by various groups found that at low  $T_{\rm g}$  or high  $P_{\rm AsH3}$  a (2×2) reconstruction takes place, which features a chemically stable As-trimer structure leading to reduced growth rate in the  $\langle 111 \rangle$ B direction, and at high  $T_{\rm g}$  or low  $P_{\rm AsH3}$  ( $\sqrt{19} \times \sqrt{19}$ ) reconstruction appears. Nishida *et al.* reported the same phase transition on the GaAs (111)B surface during MOCVD growth.

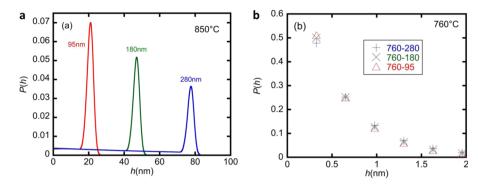

The growth condition not only changes the nucleation behavior but also affects the crystal structure in terms of twin defects. Ikejiri et al. proposed a hypothetical growth model of GaAs shape evolution in the early growth stage during SAG MOCVD. 115 In our work, we have verified Ikejiri's growth model and can explain the twin formation mechanism by direct observation of nanowire morphologies corresponding to each evolution stage. Using our five-step growth method, the highest nanowire growth temperature was 800 °C. Above this temperature, few GaAs nanowires were observed to grow from the Si<sub>3</sub>N<sub>4</sub> mask opening (see Supporting Information, Figure S2a), and we believe the reason is that at temperatures above 800 °C the desorption of the reaction species from the Si<sub>3</sub>N<sub>4</sub> and Si surface is so rapid that little deposition of GaAs could occur. However, we were able to grow nanowires at 850 °C by starting the growth at 760 °C for 5 min and then quickly ramping up the temperature to 850 °C, as the growth at 760 °C would lead to GaAs nanowires in the openings, and then even at 850 °C, the reaction species can wet the GaAs nanowires better than the Si<sub>3</sub>N<sub>4</sub> and Si surface, thus leading to growth

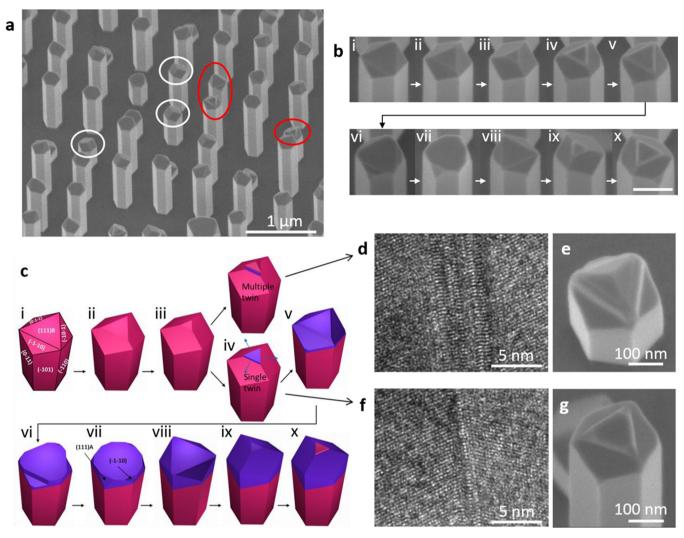

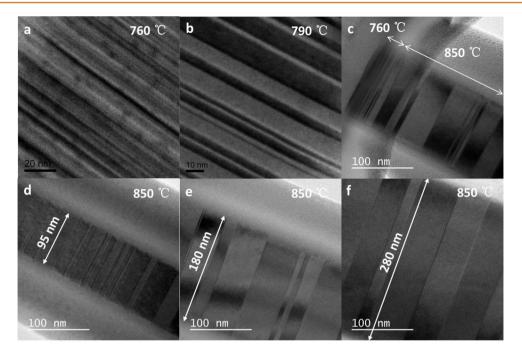

Figure 4. (a-c) TEM images of nanowires grown at different temperatures: (a) 760 °C, (b) 790 °C, and (c) 850 °C. The initial segment in (c) was grown at 760 °C in order to nucleate. (d-f) TEM images of nanowires grown at 850 °C with different diameters: (d) 95 nm, (e) 180 nm, and (f) 280 nm. (g) Histogram showing length distribution of twin-free segments of nanowires grown at 850 °C with different diameters.

even at 850 °C. Yet, as shown in Figure 3a, nanowires become much less uniform in height probably due to the longer Ga diffusion length at higher temperature, and the increased desorption rate may also influence the nonuniformities observed during growth at temperatures above 800 °C. Uneven nanowire tops appear with tilted  $\{-1-10\}$  facets and other low-index facets to various degrees. Some nanowires have a completely pinched-off tetrahedron tip (enclosed in white circles in Figure 3a), while some others have a triangularshaped thin mesa surrounded by three tilted  $\{-1-10\}$  facets (enclosed in red circles in Figure 3a). On the basis of the various nanowire tip morphologies (Figure 3b), we demonstrate the various growth fronts and the mechanism driving the twin formation. At a temperature as high as 850 °C, the growth rate in the  $\langle -1-10 \rangle$  directions is extremely low. When a nanowire grows in the vertical (111)B direction, the three tilted  $\{-1-10\}$  facets extend toward the center from three corners at the tip. Hence, the top (111)B facet is intersected by these three facets and appears to be a triangle (Figure 3c, stage i). This triangle keeps shrinking, while the  $\{-1-10\}$  facets further extend (Figure 3c, stage ii). When the triangle reaches a certain critical dimension, the probability of forming a rotational twin,

upon the deposition of the next layer, would be dramatically increased (Figure 3c, stage iii). The critical dimension of the triangle is related to the change of the Gibbs free energy for the growth of the next bilayer of the triangular area. In smaller triangles (i.e., larger peripheral/area ratios), the smaller peripheral energy density of the rotated stacking, compared to that of the normal zinc-blende stacking, makes twin formation energetically more favorable. Mathematical details of the nucleation-growth model will be provided later in this article. If no twin forms, the tip will pinch off and the nanowire growth terminates. Otherwise the triangular (111)B facet will stop shrinking but expand laterally as a mesa instead after a twin is introduced (Figure 3c, stage iv). 98,99 When a twin is formed at the interface of the nucleus and the substrate, the crystal lattice of the nucleus can be considered to be rotated by 60° (or 180° given the 3-fold symmetry) azimuthally in relation to that of the substrate. The tilted  $\langle -1-10 \rangle$  directions of the substrate are thus no longer the same slow-growth directions for the nucleus, and the lateral growth rate in those directions become considerable. The twinned mesa will fill up all the space above the original  $\{-1-10\}$  facets, making the nanowire top flat (Figure 3c, stages v to vii). Sometimes another slow-

growing facet, the (111)A facet, will appear temporarily before the mesa forms a complete flat hexagonal top (Figure 3c, stage vii). When the growth proceeds, three  $\{-1-10\}$  facets of the newly grown crystal above the twin will start to emerge at the three corners, different from those where the original  $\{-1-10\}$ facets stem. At this point, the (111)B facet starts to shrink again and the growth will repeat the whole process mentioned above. Through this repeating growth sequence, quasiperiodic twins are introduced during the nanowire growth. We also notice that around the critical size of the (111)B triangle the twinned mesa is metastable. After the first twin forms, multiple consecutive twins are also highly likely to take place. If even numbers of the twins form before the mesa eventually stabilizes, the new stable crystal shares the same lattice orientation as the original crystal underneath the first twin (TEM image in Figure 3d). Thus, three  $\{-1-10\}$  facets emerge from the edges of the triangle mesa and would finally pinch off the tip (Figure 3e). Similar to the effect of a single twin, an odd number of twins will rotate the lattice by 60° (TEM image in Figure 3f) and allow the stabilized mesa to expand laterally (Figure 3g).

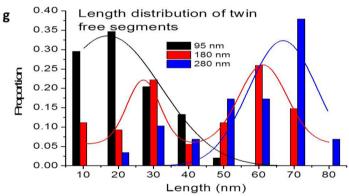

According to the growth model, the twin density or length of a twin-free segment is determined by how soon a flat hexagonal (111)B top surface shrinks to the triangle of critical dimension. In other words, the critical triangle size and the nanowire diameter together determine the length of a single twin-free segment. Figure 4a to c are TEM images of nanowires grown at different temperatures, and the different crystal orientations between two segments separated by a twin are manifested by the brightness contrast. Distinct twin densities indicate strong temperature dependence of the growth characteristics. For nanowires grown at 760 °C (Figure 4a), twins form every few monolayers, while twin-free segments can extend longer than 10 nm in nanowires grown at 790 °C (Figure 4b and Supporting Information Figure S3). The difference is even more striking in Figure 4c, where we have the initial part grown at 760 °C and later part grown at 850 °C. An abrupt interface exists, across which the twin density changes dramatically. A strong correlation between the growth temperature and the twin density is demonstrated. As one can see in the Supporting Information (Figure S4), the twins in the initial part are so dense that in many cases they form every monolayer, which makes the crystal effective in the wurtzite structure. As will be discussed in detail later, higher temperature features a smaller critical dimension, while in the case of lower temperature, the probability of forming a twin is considerable even when the (111)B facet is fairly large.

Because the probability of forming a twin increases when the tip is around the critical dimension, a larger diameter would also favor fewer twins, as it takes longer for the tip to reach that critical size. Our observation of twin-free segments on nanowires with different diameters grown at the same temperature is consistent with the observation by Yoshida et al. 98 Yoshida's work indicates that the thickness of the twin-free segments decreases as the nanowire diameter decreases. They used nanowires with 200 and 380 nm diameters and showed that the twin occurrence probability per monolayer for the 200 nm diameter nanowires is higher than that for 380 nm diameter nanowires. The largest thickness of twin-free segments is ~42 monolayers, corresponding to ~14 nm in length. In our work, nanowires were all grown at 850 °C with 95, 180, and 280 nm diameters controlled by the size of the opening in the silicon nitride mask. Figure 4d to f are the TEM pictures of these nanowires with different diameters (95 nm for Figure 4d, 180

nm for Figure 4e, and 280 nm for Figure 4f). Although they were all grown at the same temperature, the length distributions of twin-free segments are substantially different. As shown by the statistics in Figure 4g, the length of the twin-free segment becomes larger with increasing diameter. The average twin-free lengths for nanowires of 95, 180, and 280 nm diameters are 17.9, 39.1, and 53.1 nm, respectively. Gaussian peak fittings are superimposed on the histogram to show that the peaks shift toward larger twin-free length with increasing diameters. The nature of the twin peaks for the 180 nm nanowire is not fully understood at this point. The longest twin-free segment comes from our 280 nm sample, with a twin-free length of 80 nm. This twin-free length of 80 nm in GaAs nanowires using SAG is a significant improvement compared to previous work. We attribute our improvement in the twin-free length to the unusually high growth temperature (850 °C) we can achieve.

On the basis of the growth model mentioned earlier, the maximum length of a twin-free segment occurs when the tip is completely pinched off. According to the geometry of the tetrahedron enclosed by three  $\{-1-10\}$  facets, the maximum length would be 33.6, 63.6, and 99 nm for nanowires of 95, 180, and 280 nm diameters. All the lengths we measured are below the theoretical limit, with only one exception, for the 95 nm nanowire, as can be seen in Figure 4g (one data point is between 40 and 50 nm). This discrepancy could be due to the fact that the TEM sample might not have been cut right through the center of the nanowire, so the actual diameter is larger than what we observed. We also assumed zero growth rate in the  $\langle -1-10 \rangle$  directions, while in the real situation a finite growth rate cannot be ruled out.

To interpret the effects of growth temperature and diameter, we have calculated the twin-free segment length probability distribution P(h) using a simple nucleation—growth model. We considered a hexagonal GaAs nanowire with diameter D, in which a new twin-free segment starts to grow at height h=0 to form a tetrahedral island on the (111)B top surface. At height h, the next GaAs bilayer of area A(h) can grow with either the zinc-blende (zb) or fault (f) stacking. The change of the Gibbs free energy for the growth of the next bilayer of area A is given by

$$G_0^{\lambda}(A) = \left[\varepsilon_{\text{area}}^{\lambda} - \mu_{\text{gas}}(T)\right]A + \varepsilon_{\text{edge}}^{\lambda}\sqrt{A} \ (\lambda = \text{zb or f})$$

(1)

where  $\varepsilon_{\rm area}^{\lambda}$  and  $\varepsilon_{\rm edge}^{\lambda}$  are the areal and peripheral energy densities of the bilayer and  $\mu_{\rm gas}(T)$  is the chemical potential of the vapor, which depends on the temperature T in addition to the vapor pressures of the reactant gases.  $^{87}$   $G_0^{\lambda}(A)$  takes a maximum value,  $G_*^{\lambda} = G_0^{\lambda}(A^*)$ , at a critical area  $A^*$ . We note that  $\mu_{\rm gas}(T)$  decreases with increasing temperature, so the critical area  $A^*$  also decreases with increasing temperature, leading to increased twin-free segments. The Gibbs free energy used to obtain the twin statistics is then

$$G^{\lambda}(h) = \begin{cases} G_0^{\lambda}(A(h)) & (A(h) \le A^*) \\ G_*^{\lambda} & (A(h) > A^*) \end{cases}$$

$$(\lambda = \mathsf{zb}, \text{ or } \lambda = \mathsf{f} \text{ when } A(h) > A^*) \tag{2}$$

In the case of fault bilayers (where the twin boundaries are  $\lambda$  = f and  $A(h) \leq A^*$ ), we also need to take into account the twin—twin interaction,

$$G^{f}(h) = G_0^{f}(h) + \varepsilon_{int}(h) A(h)$$

(3)

Figure 5. Probability distribution of the twin-free segment length in GaAs nanowires of diameters 95, 180, and 280 nm at (a) 850  $^{\circ}$ C and (b) 760  $^{\circ}$ C.

where  $\varepsilon_{\text{int}}(h)$  is the twin–twin interaction energy density. The probability to find a twin at height h is calculated as

$$p(h) = \frac{\exp[-G^{f}(h)/k_{B}T]}{\exp[-G^{f}(h)/k_{B}T] + \exp[-G^{zb}(h)/k_{B}T]}$$

(4)

where  $k_{\rm B}$  is the Boltzmann constant, and  $G^{\rm zb}(h)$  and  $G^{\rm f}(h)$  are calculated using eqs 2 and 3, respectively, as the twins occur at  $A(h) \leq A^*$ . The probability for the first occurrence of a stacking fault at the *n*th bilayer is then

$$P(n\Delta) = \prod_{i=1}^{n-1} [1 - p(i\Delta)]p(n\Delta)$$

(5)

where  $\Delta$  is the distance between consecutive bilayers.

Figure 5 shows the calculated P(h) for three diameters, D = 95, 180, and 280 nm, at temperatures T = 850 °C and T = 760 °C. At T = 850 °C, the calculated distribution in Figure 5a exhibits a sharp peak for every diameter, where the peak position is an increasing function of D. Accordingly, the average twin-free segment length is 19, 37, and 53 nm for D = 95, 180, and 280 nm, in reasonable agreement with the experimental observations. In contrast, at a lower T = 760 °C, when the twin-free segment is expected to be much shorter, the distribution is nearly independent of D and decays rapidly to zero within the first few bilayers, as can be seen in Figure 5b.

## **CONCLUSION**

We have reported facile five-step heteroepitaxial growth of GaAs nanowires on Si (111) substrates using SAG MOCVD. Highly uniform nanowire arrays could be obtained without lowtemperature surface treatment in arsine before nanowire growth. The effects of growth temperature and arsine partial pressure were carefully studied during the initial nucleation process for GaAs nanowires on Si. We are able to grow nanowires at unusually high temperature (850 °C) and obtain a variety of tip morphologies to demonstrate the twin formation mechanism. A twin-free length up to 80 nm in our GaAs nanowires grown at 850 °C with 280 nm diameter is a significant improvement compared to previous work. The temperature dependence as well as diameter dependence were well interpreted by a mechanism of faceted growth and nucleation thermodynamics. The results deepen our understanding of twin defects frequently observed in nanowires and could open up great opportunities of heterostructure devices requiring epitaxial III-V material on a Si substrate.

#### **METHODS**

Nanowire Growth. A silicon nitride layer was first deposited on double-side polished epi-ready Si (111) substrates using plasmaenhanced chemical vapor deposition. EBL (Raith eLine Plus) or photolithography (ASML S500/300 DUV Stepper) followed by dry (CF<sub>4</sub>) or wet etching opens up an array of openings in the silicon nitride layer. No difference in vertical nanowire yield was observed between dry and wet etching. Uniform nanowire arrays could even be obtained on substrates with CF<sub>4</sub> overetched into Si by 5 nm. After resist strip-off and oxygen plasma cleaning, samples were quickly dipped in 7:1 buffered oxide etchant for 3 s, blown dry with nitrogen, and immediately loaded into MOCVD reactor. Nanowires were then grown in a vertical Thomas Swan MOCVD showerhead reactor at 0.1 atm pressure. Trimethylgallium and arsine were used as the precursors for Ga and As. The total flow rate of the carrier gas was 7 standard liters per minute, and partial pressures for TMG and AsH<sub>3</sub> are 7.56 ×  $10^{-7}$  and  $2.14 \times 10^{-4}$  atm unless otherwise stated. Prior to actual nanowire growth, the substrate was annealed in hydrogen ambient for 5 min at 925 °C. We found this step to be essential, as growth with hydrogen annealing at lower temperature results in an increased number of irregular growths (see Supporting Information Figure S5). The temperature was then decreased to nanowire growth temperature between 700 and 790 °C, and the TMG and AsH<sub>3</sub> precursors were introduced simultaneously. After growth the TMG was interrupted, while AsH<sub>3</sub> continued to flow until the temperature is below 300 °C to prevent decomposition of the GaAs at high temperature.

## **ASSOCIATED CONTENT**

#### S Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsnano.5b07232.

Details on GaAs nanowire arrays grown on Si with different hydrogen annealing temperatures, with and without low-temperature surface treatment, SEM images of Ga diffusion at different growth temperatures, distribution of twin-free segment length in nanowires grown at 790 °C, and a high-resolution TEM image at the interface of Si and GaAs for 850 °C growth temperature with 760 °C buffer growth sample (PDF)

## **AUTHOR INFORMATION**

### **Corresponding Authors**

\*E-mail: (C. Zhou) chongwuz@usc.edu. \*E-mail: (P. D. Dapkus) dapkus@usc.edu.

#### Notes

The authors declare no competing financial interest.

## **ACKNOWLEDGMENTS**

This material is based upon work supported as part of the Center for Energy Nanoscience (CEN), an Energy Frontier Research Center (EFRC) funded by the U.S. Department of Energy, Office of Science and Office of Basic Energy Sciences, under Award Number DE-SC0001013. Computing resources were provided by the USC Center for High Performance Computing and Communications. M.Y. was funded by a USC Provost's Ph.D. Fellowship.

## **REFERENCES**

- (1) Huang, Y.; Duan, X.; Cui, Y.; Lauhon, L. J.; Kim, K.-H.; Lieber, C. M. Logic Gates and Computation from Assembled Nanowire Building Blocks. *Science* **2001**, *294*, 1313–1317.

- (2) Gudiksen, M. S.; Lauhon, L. J.; Wang, J.; Smith, D. C.; Lieber, C. M. Growth of Nanowire Superlattice Structures for Nanoscale Photonics and Electronics. *Nature* **2002**, *415*, 617–620.

- (3) Lauhon, L. J.; Gudiksen, M. S.; Wang, D.; Lieber, C. M. Epitaxial Core-Shell and Core-Multishell Nanowire Heterostructures. *Nature* **2002**, 420, 57–61.

- (4) Johnson, J. C.; Choi, H.-J.; Knutsen, K. P.; Schaller, R. D.; Yang, P.; Saykally, R. J. Single Gallium Nitride Nanowire Lasers. *Nat. Mater.* **2002**, *1*, 106–110.

- (5) Parkinson, P.; Lloyd-Hughes, J.; Gao, Q.; Tan, H. H.; Jagadish, C.; Johnston, M. B.; Herz, L. M. Transient Terahertz Conductivity of GaAs Nanowires. *Nano Lett.* **2007**, *7*, 2162–2165.

- (6) Tang, T.; Han, S.; Jin, W.; Liu, X. L.; Li, C.; Zhang, D. H.; Zhou, C. W.; Chen, B.; Han, J.; Meyyapan, M. Synthesis and Characterization of Single-Crystal Indium Nitride Nanowires. *J. Mater. Res.* 2004, 19, 423–426.

- (7) Lei, B.; Li, C.; Zhang, D. H.; Zhou, Q. F.; Shung, K. K.; Zhou, C. W. Nanowire Transistors with Ferroelectric Gate Dielectrics: Enhanced Performance and Memory Effects. *Appl. Phys. Lett.* **2004**, 4553—4555

- (8) Li, C.; Lei, B.; Zhang, D. H.; Liu, X. L.; Han, S.; Tang, T.; Rouhanizadeh, M.; Hsiai, T.; Zhou, C. W. Chemical Gating of In2O3 Nanowires by Organic and Biomolecules. *Appl. Phys. Lett.* **2003**, 83, 4014–4016.

- (9) Thelander, C.; FrobergFroberg, L. E.; Rehnstedt, C.; Samuelson, L.; Wernersson, L. E. Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor With 50-nm Wrap Gate. *IEEE Electron Device Lett.* 2008, 29, 206–208.

- (10) Tomioka, K.; Yoshimura, M.; Fukui, T. A III-V Nanowire Channel on Silicon for High-Performance Vertical Transistors. *Nature* **2012**, 488, 189–192.

- (11) Dayeh, S. A.; Aplin, D. P. R.; Zhou, X.; Yu, P. K. L.; Yu, E. T.; Wang, D. High Electron Mobility InAs Nanowire Field-Effect Transistors. *Small* **2007**, *3*, 326–332.

- (12) Egard, M.; Johansson, S.; Johansson, A. C.; Persson, K. M.; Dey, A. W.; Borg, B. M.; Thelander, C.; Wernersson, L. E.; Lind, E. Vertical InAs Nanowire Wrap Gate Transistors with ft > 7 GHz and fmax > 20 GHz. *Nano Lett.* **2010**, *10*, 809–812.

- (13) Kasai, S.; Hasegawa, H. GaAs and InGaAs Single Electron Hexagonal Nanowire Circuits Based on Binary Decision Diagram Logic Architecture. *Phys. E* **2002**, *13*, 925–929.

- (14) Thelander, C.; Mårtensson, T.; Björk, M. T.; Ohlsson, B. J.; Larsson, M. W.; Wallenberg, L. R.; Samuelson, L. Single-Electron Transistors in Heterostructure Nanowires. *Appl. Phys. Lett.* **2003**, 83, 2052–2054.

- (15) Bryllert, T.; Wernersson, L. E.; Froberg, L. E.; Samuelson, L. Vertical High-Mobility Wrap-Gated InAs Nanowire Transistor. *IEEE Electron Device Lett.* **2006**, *27*, 323–325.

- (16) Ng, H. T.; Han, J.; Yamada, T.; Nguyen, P.; Chen, Y. P.; Meyyappan, M. Single Crystal Nanowire Vertical Surround-Gate Field-Effect Transistor. *Nano Lett.* **2004**, *4*, 1247–1252.

- (17) Thelander, C.; Nilsson, H. A.; Jensen, L. E.; Samuelson, L. Nanowire Single-Electron Memory. *Nano Lett.* **2005**, *5*, 635–638.

- (18) Svensson, C. P. T.; Mårtensson, T.; Trägårdh, J.; Larsson, C.; Rask, M.; Hessman, D.; Samuelson, L.; Ohlsson, J. Monolithic GaAs/InGaP Nanowire Light Emitting Diodes on Silicon. *Nanotechnology* **2008**, *19*, 305201.

- (19) Guo, W.; Zhang, M.; Banerjee, A.; Bhattacharya, P. Catalyst-Free InGaN/GaN Nanowire Light Emitting Diodes Grown on (001) Silicon by Molecular Beam Epitaxy. *Nano Lett.* **2010**, *10*, 3355–3359.

- (20) Mayer, B.; Rudolph, D.; Schnell, J.; Morkötter, S.; Winnerl, J.; Treu, J.; Müller, K.; Bracher, G.; Abstreiter, G.; Koblmüller, G.; Finley, J. J. Lasing from Individual GaAs-AlGaAs Core-Shell Nanowires up to Room Temperature. *Nat. Commun.* **2013**, *4*, 2931.

- (21) Saxena, D.; Mokkapati, S.; Parkinson, P.; Jiang, N.; Gao, Q.; Tan, H. H.; Jagadish, C. Optically Pumped Room-Temperature GaAs Nanowire Lasers. *Nat. Photonics* **2013**, *7*, 963–968.

- (22) Yan, R.; Gargas, D.; Yang, P. Nanowire Photonics. *Nat. Photonics* **2009**, *3*, 569–576.

- (23) Huang, M. H.; Mao, S.; Feick, H.; Yan, H.; Wu, Y.; Kind, H.; Weber, E.; Russo, R.; Yang, P. Room-Temperature Ultraviolet Nanowire Nanolasers. *Science* **2001**, 292, 1897–1899.

- (24) Qian, F.; Li, Y.; Gradecak, S.; Park, H.-G.; Dong, Y.; Ding, Y.; Wang, Z. L.; Lieber, C. M. Multi-Quantum-Well Nanowire Heterostructures for Wavelength-Controlled Lasers. *Nat. Mater.* **2008**, *7*, 701–706.

- (25) Duan, X.; Huang, Y.; Agarwal, R.; Lieber, C. M. Single-Nanowire Electrically Driven Lasers. *Nature* **2003**, *421*, 241–245.

- (26) Pettersson, H.; Trägårdh, J.; Persson, A. I.; Landin, L.; Hessman, D.; Samuelson, L. Infrared Photodetectors in Heterostructure Nanowires. *Nano Lett.* **2006**, *6*, 229–232.

- (27) Seyedi, M. A.; Yao, M.; O'Brien, J.; Wang, S. Y.; Dapkus, P. D. Large Area, Low Capacitance, GaAs Nanowire Photodetector with a Transparent Schottky Collecting Junction. *Appl. Phys. Lett.* **2013**, *103*, 251109.

- (28) Tomioka, K.; Motohisa, J.; Hara, S.; Hiruma, K.; Fukui, T. GaAs/AlGaAs Core Multishell Nanowire-Based Light-Emitting Diodes on Si. *Nano Lett.* **2010**, *10*, 1639–1644.

- (29) Mariani, G.; Scofield, A. C.; Hung, C.-H.; Huffaker, D. L. GaAs Nanopillar-Array Solar Cells Employing *in situ* Surface Passivation. *Nat. Commun.* **2013**, *4*, 1497.

- (30) Wallentin, J.; Anttu, N.; Asoli, D.; Huffman, M.; Åberg, I.; Magnusson, M. H.; Siefer, G.; Fuss-Kailuweit, P.; Dimroth, F.; Witzigmann, B.; Xu, H. Q.; Samuelson, L.; Deppert, K.; Borgström, M. T. InP Nanowire Array Solar Cells Achieving 13.8% Efficiency by Exceeding the Ray Optics Limit. *Science* **2013**, 339, 1057–1060.

- (31) Cui, Y.; Wang, J.; Plissard, S. R.; Cavalli, A.; Vu, T. T. T.; van Veldhoven, R. P. J.; Gao, L.; Trainor, M.; Verheijen, M. A.; Haverkort, J. E. M.; Bakkers, E. P. A. M. Efficiency Enhancement of InP Nanowire Solar Cells by Surface Cleaning. *Nano Lett.* **2013**, *13*, 4113–4117.

- (32) Hu, S.; Chi, C.-Y.; Fountaine, K. T.; Yao, M.; Atwater, H. A.; Dapkus, P. D.; Lewis, N. S.; Zhou, C. Optical, Electrical, and Solar Energy-Conversion Properties of Gallium Arsenide Nanowire-Array Photoanodes. *Energy Environ. Sci.* 2013, *6*, 1879–1890.

- (33) Yao, M.; Huang, N.; Cong, S.; Chi, C.-Y.; Seyedi, M. A.; Lin, Y.-T.; Cao, Y.; Povinelli, M. L.; Dapkus, P. D.; Zhou, C. GaAs Nanowire Array Solar Cells with Axial p—i—n Junctions. *Nano Lett.* **2014**, *14*, 3293—3303.

- (34) LaPierre, R. R. Theoretical Conversion Efficiency of a Two-Junction III-V Nanowire on Si Solar Cell. *J. Appl. Phys.* **2011**, *110*, 014310.

- (35) Huang, N.; Lin, C.; Povinelli, M. L. Limiting Efficiencies of Tandem Solar Cells Consisting of III-V Nanowire Arrays on Silicon. *J. Appl. Phys.* **2012**, *112*, 064321.

- (36) Yao, M. Q.; Cong, S.; Arab, S.; Huang, N. F.; Povinelli, M. L.; Cronin, S. B.; Dapkus, P. D.; Zhou, C. W. Tandem Solar Cells Using GaAs Nanowires on Si: Design, Fabrication, and Observation of Voltage Addition. *Nano Lett.* **2015**, *15*, 7217–7224.

- (37) Fang, S. F.; Adomi, K.; Iyer, S.; Morkoç, H.; Zabel, H.; Choi, C.; Otsuka, N. Gallium Arsenide and Other Compound Semiconductors on Silicon. *J. Appl. Phys.* **1990**, *68*, R31–R58.

(38) Ishiwara, H.; Hoshino, T.; Katahama, H. Formation of Strain-Free GaAs-on-Si Structures by Annealing Under Ultrahigh Pressure. *Mater. Chem. Phys.* **1995**, *40*, 225–229.

- (39) Cohen, D.; Carter, C. B. Structure of the (110) Antiphase Boundary in Gallium Phosphide. *J. Microsc.* **2002**, 208, 84–99.

- (40) Komninou, P.; Stoemenos, J.; Dimitrakopulos, G. P.; Karakostas, T. Misfit Dislocations and Antiphase Domain Boundaries in GaAs/Si Interface. *J. Appl. Phys.* **1994**, *75*, 143–152.

- (41) Bolkhovityanov, Y. B.; Pchelyakov, O. P. GaAs Epitaxy on Si Substrates: Modern Status of Research and Engineering. *Phys.-Usp.* **2008**, *51*, 437.

- (42) Kawanami, H. Heteroepitaxial Technologies of III–V on Si. Sol. Energy Mater. Sol. Cells 2001, 66, 479–486.

- (43) Mårtensson, T.; Svensson, C. P. T.; Wacaser, B. A.; Larsson, M. W.; Seifert, W.; Deppert, K.; Gustafsson, A.; Wallenberg, L. R.; Samuelson, L. Epitaxial III–V Nanowires on Silicon. *Nano Lett.* **2004**, *4*, 1987–1990.

- (44) Tomioka, K.; Kobayashi, Y.; Motohisa, J.; Hara, S.; Fukui, T. Selective-Area Growth of Vertically Aligned GaAs and GaAs/AlGaAs Core-Shell Nanowires on Si(111) Substrate. *Nanotechnology* **2009**, *20*, 145302.

- (45) Tomioka, K.; Motohisa, J.; Hara, S.; Fukui, T. Control of InAs Nanowire Growth Directions on Si. *Nano Lett.* **2008**, *8*, 3475–3480.

- (46) Glas, F. Critical Dimensions for the Plastic Relaxation of Strained Axial Heterostructures in Free-Standing Nanowires. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2006**, 74, 121302.

- (47) Chuang, L. C.; Moewe, M.; Chase, C.; Kobayashi, N. P.; Chang-Hasnain, C.; Crankshaw, S. Critical Diameter for III-V Nanowires Grown on Lattice-Mismatched Substrates. *Appl. Phys. Lett.* **2007**, *90*, 043115.

- (48) Sburlan, S.; Dapkus, P. D.; Nakano, A. Critical Dimensions of Highly Lattice Mismatched Semiconductor Nanowires Grown in Strain-Releasing Configurations. *Appl. Phys. Lett.* **2012**, *100*, 163108.

- (49) Cirlin, G. E.; Dubrovskii, V. G.; Soshnikov, I. P.; Sibirev, N. V.; Samsonenko, Y. B.; Bouravleuv, A. D.; Harmand, J. C.; Glas, F. Critical Diameters and Temperature Domains for MBE Growth of III–V Nanowires on Lattice Mismatched Substrates. *Phys. Status Solidi RRL* **2009**, *3*, 112–114.

- (50) Hertenberger, S.; Funk, S.; Vizbaras, K.; Yadav, A.; Rudolph, D.; Becker, J.; Bolte, S.; Döblinger, M.; Bichler, M.; Scarpa, G.; Lugli, P.; Zardo, I.; Finley, J. J.; Amann, M.-C.; Abstreiter, G.; Koblmüller, G. High Compositional Homogeneity in In-Rich InGaAs Nanowire Arrays on Nanoimprinted SiO<sub>2</sub>/Si (111). *Appl. Phys. Lett.* **2012**, *101*, 043116.

- (51) Krogstrup, P.; Popovitz-Biro, R.; Johnson, E.; Madsen, M. H.; Nygård, J.; Shtrikman, H. Structural Phase Control in Self-Catalyzed Growth of GaAs Nanowires on Silicon (111). *Nano Lett.* **2010**, *10*, 4475–4482.

- (52) Munshi, A. M.; Dheeraj, D. L.; Todorovic, J.; van Helvoort, A. T. J.; Weman, H.; Fimland, B.-O. Crystal Phase Engineering in Self-Catalyzed GaAs and GaAs/GaAsSb Nanowires Grown on Si(111). *J. Cryst. Growth* **2013**, 372, 163–169.

- (53) Cirlin, G. E.; Dubrovskii, V. G.; Samsonenko, Y. B.; Bouravleuv, A. D.; Durose, K.; Proskuryakov, Y. Y.; Mendes, B.; Bowen, L.; Kaliteevski, M. A.; Abram, R. A.; Zeze, D. Self-Catalyzed, Pure Zincblende GaAs Nanowires Grown on Si(111) by Molecular Beam Epitaxy. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2010**, *82*, 035302.

- (54) Gibson, S. J.; Boulanger, J. P.; Lapierre, R. R. Opportunities and Pitfalls in Patterned Self-Catalyzed GaAs Nanowire Growth on Silicon. *Semicond. Sci. Technol.* **2013**, 28, 105025.

- (55) Jabeen, F.; Grillo, V.; Rubini, S.; Martelli, F. Self-Catalyzed Growth of GaAs Nanowires on Cleaved Si by Molecular Beam Epitaxy. *Nanotechnology* **2008**, *19*, 275711.

- (56) Mandl, B.; Stangl, J.; Mårtensson, T.; Mikkelsen, A.; Eriksson, J.; Karlsson, L. S.; Bauer, G.; Samuelson, L.; Seifert, W. Au-Free Epitaxial Growth of InAs Nanowires. *Nano Lett.* **2006**, *6*, 1817–1821.

- (57) Paek, J. H.; Nishiwaki, T.; Yamaguchi, M.; Sawaki, N. Catalyst Free MBE-VLS Growth of GaAs Nanowires on (111)Si Substrate. *Phys. Status Solidi C* **2009**, *6*, 1436–1440.

- (58) Bao, X.-Y.; Soci, C.; Susac, D.; Bratvold, J.; Aplin, D. P. R.; Wei, W.; Chen, C.-Y.; Dayeh, S. A.; Kavanagh, K. L.; Wang, D. Heteroepitaxial Growth of Vertical GaAs Nanowires on Si (111) Substrates by Metal—Organic Chemical Vapor Deposition. *Nano Lett.* **2008**, *8*, 3755—3760.

- (59) Wei, W.; Bao, X.-Y.; Soci, C.; Ding, Y.; Wang, Z.-L.; Wang, D. Direct Heteroepitaxy of Vertical InAs Nanowires on Si Substrates for Broad Band Photovoltaics and Photodetection. *Nano Lett.* **2009**, *9*, 2926–2934.

- (60) Roest, A. L.; Verheijen, M. A.; Wunnicke, O.; Serafin, S.; Wondergem, H.; Bakkers, E. P. A. M. Position-Controlled Epitaxial III–V Nanowires on Silicon. *Nanotechnology* **2006**, *17*, S271.

- (61) Ihn, S.-G.; Song, J.-I.; Kim, Y.-H.; Lee, J. Y. GaAs Nanowires on Si Substrates Grown by a Solid Source Molecular Beam Epitaxy. *Appl. Phys. Lett.* **2006**, *89*, 053106.

- (62) Huang, H.; Ren, X.; Ye, X.; Guo, J.; Wang, Q.; Yang, Y.; Cai, S.; Huang, Y. Growth of Stacking-Faults-Free Zinc Blende GaAs Nanowires on Si Substrate by Using AlGaAs/GaAs Buffer Layers. *Nano Lett.* **2009**, *10*, 64–68.

- (63) Kang, J. H.; Gao, Q.; Joyce, H. J.; Tan, H. H.; Jagadish, C.; Kim, Y.; Choi, D. Y.; Guo, Y.; Xu, H.; Zou, J.; Fickenscher, M. A.; Smith, L. M.; Jackson, H. E.; Yarrison-Rice, J. M. Novel Growth and Properties of GaAs Nanowires on Si Substrates. *Nanotechnology* **2010**, *21*, 035604.

- (64) Plissard, S.; Dick, K. A.; Wallart, X.; Caroff, P. Gold-Free GaAs/GaAsSb Heterostructure Nanowires Grown on Silicon. *Appl. Phys. Lett.* **2010**, *96*, 121901.

- (65) Munshi, A. M.; Dheeraj, D. L.; Fauske, V. T.; Kim, D. C.; Huh, J.; Reinertsen, J. F.; Ahtapodov, L.; Lee, K. D.; Heidari, B.; van Helvoort, A. T. J.; Fimland, B. O.; Weman, H. Position-Controlled Uniform GaAs Nanowires on Silicon using Nanoimprint Lithography. *Nano Lett.* **2014**, *14*, 960–966.

- (66) Plissard, S.; Dick, K. A.; Larrieu, G.; Godey, S.; Addad, A.; Wallart, X.; Caroff, P. Gold-Free Growth of GaAs Nanowires on Silicon: Arrays and Polytypism. *Nanotechnology* **2010**, *21*, 385602.

- (67) Kwoen, J.; Watanabe, K.; Iwamoto, S.; Arakawa, Y. Non-VLS Growth of GaAs Nanowires on Silicon by a Gallium Pre-Deposition technique. *J. Cryst. Growth* **2013**, 378, 562–565.

- (68) Koblmüller, G.; Hertenberger, S.; Vizbaras, K.; Bichler, M.; Bao, F.; Zhang, J. P.; Abstreiter, G. Self-Induced Growth of Vertical Free-Standing InAs Nanowires on Si(111) by Molecular Beam Epitaxy. *Nanotechnology* **2010**, *21*, 365602.

- (69) Rudolph, D.; Hertenberger, S.; Bolte, S.; Paosangthong, W.; Spirkoska, D. e.; Döblinger, M.; Bichler, M.; Finley, J. J.; Abstreiter, G.; Koblmüller, G. Direct Observation of a Noncatalytic Growth Regime for GaAs Nanowires. *Nano Lett.* **2011**, *11*, 3848–3854.

- (70) Tateno, K.; Hibino, H.; Gotoh, H.; Nakano, H. Vertical GaP Nanowires Arranged at Atomic Steps on Si(111) Substrates. *Appl. Phys. Lett.* **2006**, *89*, 033114.

- (71) Ihn, S.-G.; Song, J.-I.; Kim, T.-W.; Leem, D.-S.; Lee, T.; Lee, S.-G.; Koh, E. K.; Song, K. Morphology- and Orientation-Controlled Gallium Arsenide Nanowires on Silicon Substrates. *Nano Lett.* **2007**, *7*, 39–44.

- (72) Mårtensson, T.; Wagner, J. B.; Hilner, E.; Mikkelsen, A.; Thelander, C.; Stangl, J.; Ohlsson, B. J.; Gustafsson, A.; Lundgren, E.; Samuelson, L.; Seifert, W. Epitaxial Growth of Indium Arsenide Nanowires on Silicon Using Nucleation Templates Formed by Self-Assembled Organic Coatings. *Adv. Mater.* 2007, 19, 1801–1806.

- (73) Mohseni, P. K.; Maunders, C.; Botton, G. A.; LaPierre, R. R. GaP/GaAsP/GaP Core—Multishell Nanowire Heterostructures on (111) Silicon. *Nanotechnology* **2007**, *18*, 445304.

- (74) Paek, J. H.; Nishiwaki, T.; Yamaguchi, M.; Sawaki, N. MBE-VLS Growth of GaAs Nanowires on (111)Si Substrate. *Phys. Status Solidi C* **2008**, *5*, 2740–2742.

- (75) Tomioka, K.; Fukui, T. Tunnel Field-Effect Transistor Using InAs Nanowire/Si Heterojunction. *Appl. Phys. Lett.* **2011**, 98, 083114.

- (76) Yang, T.; Hertenberger, S.; Morkotter, S.; Abstreiter, G.; Koblmuller, G. Size, Composition, and Doping Effects on In(Ga)As

Nanowire/Si Tunnel Diodes Probed by Conductive Atomic Force Microscopy. Appl. Phys. Lett. 2012, 101, 233102.

- (77) Heurlin, M.; Wickert, P.; Fält, S.; Borgström, M. T.; Deppert, K.; Samuelson, L.; Magnusson, M. H. Axial InP Nanowire Tandem Junction Grown on a Silicon Substrate. *Nano Lett.* **2011**, *11*, 2028–2031.

- (78) Wagner, R. S.; Ellis, W. C. Vapor-Liquid-Solid Mechanism of Single Crystal Growth. *Appl. Phys. Lett.* **1964**, *4*, 89–90.

- (79) Bar-Sadan, M.; Barthel, J.; Shtrikman, H.; Houben, L. Direct Imaging of Single Au Atoms Within GaAs Nanowires. *Nano Lett.* **2012**, *12*, 2352–2356.

- (80) Perea, D. E.; Allen, J. E.; May, S. J.; Wessels, B. W.; Seidman, D. N.; Lauhon, L. J. Three-Dimensional Nanoscale Composition Mapping of Semiconductor Nanowires. *Nano Lett.* **2005**, *6*, 181–185.

- (81) Allen, J. E.; Hemesath, E. R.; Perea, D. E.; Lensch-Falk, J. L.; LiZ, Y.; Yin, F.; Gass, M. H.; Wang, P.; Bleloch, A. L.; Palmer, R. E.; Lauhon, L. J. High-Resolution Detection of Au Catalyst Atoms in Si Nanowires. *Nat. Nanotechnol.* **2008**, *3*, 168–173.

- (82) Breuer, S.; Pfüller, C.; Flissikowski, T.; Brandt, O.; Grahn, H. T.; Geelhaar, L.; Riechert, H. Suitability of Au- and Self-Assisted GaAs Nanowires for Optoelectronic Applications. *Nano Lett.* **2011**, *11*, 1276–1279.

- (83) Fukui, T.; Yoshimura, M.; Nakai, E.; Tomioka, K. Position-Controlled III–V Compound Semiconductor Nanowire Solar Cells by Selective-Area Metal—Organic Vapor Phase Epitaxy. *Ambio* **2012**, *41*, 119–124.

- (84) Parkinson, P.; Joyce, H. J.; Gao, Q.; Tan, H. H.; Zhang, X.; Zou, J.; Jagadish, C.; Herz, L. M.; Johnston, M. B. Carrier Lifetime and Mobility Enhancement in Nearly Defect-Free Core—Shell Nanowires Measured Using Time-Resolved Terahertz Spectroscopy. *Nano Lett.* **2009**, *9*, 3349—3353.

- (85) Spirkoska, D.; Arbiol, J.; Gustafsson, A.; Conesa-Boj, S.; Glas, F.; Zardo, I.; Heigoldt, M.; Gass, M. H.; Bleloch, A. L.; Estrade, S.; Kaniber, M.; Rossler, J.; Peiro, F.; Morante, J. R.; Abstreiter, G.; Samuelson, L.; Fontcuberta i Morral, A. Structural and Optical Properties of High Quality Zinc-Blende/Wurtzite GaAs Nanowire Heterostructures. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2009**, *80*, 245325.

- (86) Thelander, C.; Caroff, P.; Plissard, S. b.; Dey, A. W.; Dick, K. A. Effects of Crystal Phase Mixing on the Electrical Properties of InAs Nanowires. *Nano Lett.* **2011**, *11*, 2424–2429.

- (87) Yuan, Z.; Nomura, K.-i.; Nakano, A. A Core/Shell Mechanism for Stacking-Fault Generation in GaAs Nanowires. *Appl. Phys. Lett.* **2012**, *100*, 163103.

- (88) Ikejiri, K.; Kitauchi, Y.; Tomioka, K.; Motohisa, J.; Fukui, T. Zinc Blende and Wurtzite Crystal Phase Mixing and Transition in Indium Phosphide Nanowires. *Nano Lett.* **2011**, *11*, 4314–4318.

- (89) Algra, R. E.; Verheijen, M. A.; Borgstrom, M. T.; Feiner, L.-F.; Immink, G.; van Enckevort, W. J. P.; Vlieg, E.; Bakkers, E. P. A. M. Twinning Superlattices in Indium Phosphide Nanowires. *Nature* **2008**, 456, 369–372.

- (90) Algra, R. E.; Verheijen, M. A.; Feiner, L.-F.; Immink, G. G. W.; Enckevort, W. J. P. v.; Vlieg, E.; Bakkers, E. P. A. M. The Role of Surface Energies and Chemical Potential during Nanowire Growth. *Nano Lett.* **2011**, *11*, 1259–1264.

- (91) Caroff, P.; Dick, K. A.; Johansson, J.; Messing, M. E.; Deppert, K.; Samuelson, L. Controlled Polytypic and Twin-Plane Superlattices in III-V Nanowires. *Nat. Nanotechnol.* **2009**, *4*, 50–55.

- (92) Dick, K. A.; Bolinsson, J.; Messing, M. E.; Lehmann, S.; Johansson, J.; Caroff, P. Parameter Space Mapping of InAs Nanowire Crystal Structure. *J. Vac. Sci. Technol., B* **2011**, *29*, 04D103.

- (93) Johansson, J.; Karlsson, L. S.; Svensson, C. P. T.; Martensson, T.; Wacaser, B. A.; Deppert, K.; Samuelson, L.; Seifert, W. Structural Properties of < 111 > B -Oriented III-V Nanowires. *Nat. Mater.* **2006**, *5*, 574–580.

- (94) Johansson, J.; Dick, K. A.; Caroff, P.; Messing, M. E.; Bolinsson, J.; Deppert, K.; Samuelson, L. Diameter Dependence of the Wurtzite–Zinc Blende Transition in InAs Nanowires. *J. Phys. Chem. C* **2010**, *114*, 3837–3842.

- (95) Joyce, H. J.; Wong-Leung, J.; Gao, Q.; Tan, H. H.; Jagadish, C. Phase Perfection in Zinc Blende and Wurtzite III–V Nanowires Using Basic Growth Parameters. *Nano Lett.* **2010**, *10*, 908–915.

- (96) Glas, F.; Harmand, J.-C.; Patriarche, G. Why Does Wurtzite Form in Nanowires of III-V Zinc Blende Semiconductors? *Phys. Rev. Lett.* **2007**, *99*, 146101.

- (97) Dubrovskii, V. G.; Sibirev, N. V.; Harmand, J. C.; Glas, F. Growth kinetics and crystal structure of semiconductor nanowires. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2008**, *78*, 235301.

- (98) Yoshida, H.; Ikejiri, K.; Sato, T.; Hara, S.; Hiruma, K.; Motohisa, J.; Fukui, T. Analysis of Twin Defects in GaAs Nanowires and Tetrahedra and Their Correlation to GaAs(111)B Surface Reconstructions in Selective-Area Metal Organic Vapour-Phase Epitaxy. *J. Cryst. Growth* **2009**, 312, 52–57.

- (99) Chi, C.-Y.; Chang, C.-C.; Hu, S.; Yeh, T.-W.; Cronin, S. B.; Dapkus, P. D. Twin-Free GaAs Nanosheets by Selective Area Growth: Implications for Defect-Free Nanostructures. *Nano Lett.* **2013**, *13*, 2506–2515.

- (100) Shapiro, J. N.; Lin, A.; Ratsch, C.; Huffaker, D. L. Temperature Dependence of Stacking Faults in Catalyst-Free GaAs Nanopillars. *Nanotechnology* **2013**, 24, 475601.

- (101) Yuan, Z.; Shimamura, K.; Shimojo, F.; Nakano, A. Critical Size for the Generation of Misfit Dislocations and Their Effects on Electronic Properties in GaAs Nanosheets on Si Substrate. *J. Appl. Phys.* **2013**, *114*, 074316.

- (102) Tournié, E.; Ploog, K. H. Surface Stoichiometry, Epitaxial Morphology and Strain Relaxation During Molecular Beam Epitaxy of Highly Strained InAs/Ga<sub>0.47</sub>In<sub>0.53</sub>As heterostructures. *J. Cryst. Growth* **1994**, *135*, 97–112.

- (103) Zinke-Allmang, M.; Feldman, L. C.; Nakahara, S. Initial Stages of Epitaxial Growth: Gallium Arsenide on Silicon. *Appl. Phys. Lett.* **1988**, *52*, 144–146.

- (104) Biegelsen, D. K.; Ponce, F. A.; Smith, A. J.; Tramontana, J. C. Initial Stages of Epitaxial Growth of GaAs on (100) Silicon. *J. Appl. Phys.* **1987**, *61*, 1856–1859.

- (105) Hull, R.; Fischer-Colbrie, A.; Rosner, S. J.; Koch, S. M.; Harris, J. S. Effect of Substrate Surface Structure on Nucleation of GaAs on Si(100). *Appl. Phys. Lett.* **1987**, *51*, 1723–1725.

- (106) Uhrberg, R. I. G.; Bringans, R. D.; Olmstead, M. A.; Bachrach, R. Z.; Northrup, J. E. Electronic Structure, Atomic Structure, and the Passivated Nature of the Arsenic-Terminated Si(111) Surface. *Phys. Rev. B: Condens. Matter Mater. Phys.* 1987, 35, 3945–3951.

- (107) Ando, S.; Kobayashi, N.; Ando, H. Selective-Area Metalorganic Chemical-Vapor-Deposition Growth for Hexagonal-Facet Lasers. *J. Cryst. Growth* **1994**, *145*, 302–307.

- (108) Biegelsen, D. K.; Bringans, R. D.; Northrup, J. E.; Swartz, L. E. Reconstructions of GaAs(1<sup>-</sup> 1<sup>-</sup> 1<sup>-</sup>) Surfaces Observed by Scanning Tunneling Microscopy. *Phys. Rev. Lett.* **1990**, *65*, 452–455.

- (109) Thornton, J. M. C.; Woolf, D. A.; Weightman, P. Reconstructions of the GaAs(111)B Surface. Appl. Surf. Sci. 1998, 123–124, 115–119.

- (110) Rajkumar, K. C.; Chen, P.; Madhukar, A. A Transmission Electron Microscope Study of Twin Structure in GaAs/GaAs (111)B Grown *via* Molecular Beam Epitaxy. *J. Appl. Phys.* **1991**, *69*, 2219–2223

- (111) Woolf, D. A.; Westwood, D. I.; Williams, R. H. Surface reconstructions of GaAs(111)A and (111)B: A Static Surface Phase Study by Reflection High Energy Electron Diffraction. *Appl. Phys. Lett.* **1993**, *62*, 1370–1372.

- (112) Avery, A. R.; Tok, E. S.; Jones, T. S. An STM Study of the Nature of the Transitional Phase of the GaAs(111) B Surface. *Surf. Sci.* **1997**, *376*, L397–L402.

- (113) Chen, P.; Rajkumar, K. C.; Madhukar, A. Growth Control of GaAs Epilayers with Specular Surface Free of Pyramids and Twins on Nonmisoriented (111)B Substrates. *Appl. Phys. Lett.* **1991**, *58*, 1771–1773.

- (114) Nishida, T.; Uwai, K.; Kobayashi, Y.; Kobayashi, N. Phase Diagram of GaAs (111)B Surface during Metal-Organic Chemical

Vapor Deposition Measured by Surface Photo-Absorption. Jpn. J. Appl.

Phys. 1995, 34, 6326.

(115) Ikejiri, K.; Sato, T.; Yoshida, H.; Hiruma, K.; Motohisa, J.; Hara, S.; Fukui, T. Growth Characteristics of GaAs Nanowires Obtained by Selective Area Metal-Organic Vapour-Phase Epitaxy. Nanotechnology 2008, 19, 265604.

(116) Yuan, Z.; Nakano, A. Self-Replicating Twins in Nanowires.

Nano Lett. 2013, 13, 4925-4930.